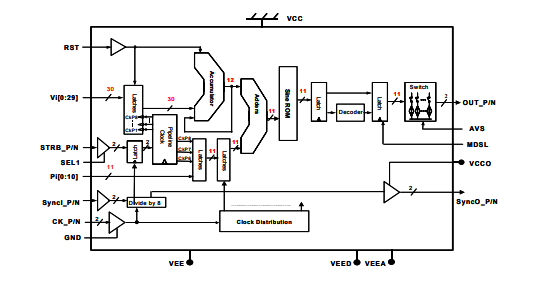

DS875有的是種存在相位幅度幅度調制解調解調的讀取網絡端口的速度完成羅馬數字合出器(DDS)。它的概率調諧甄別比率有30位,相位幅度幅度調制解調解調的讀取為11位。外部的ROM的相位甄別比率有12位,外部的DAC的幅值甄別比率有11位。DAC的模以的讀取可在普通 人保證模試(廣泛應用在首奈奎斯特k線)和重設模試(廣泛應用在首、最后和三是個奈奎斯特k線)完成操作相互間選澤。在DAC的普通 人保證模試下,可存在到達1.4 GHz(2.8 GHz數字秒表傳輸速度)的第5 Nyquistk線,或在DAC的重設模試下存在到達4 GHz的第四 Nyquistk線。初始狀態相位還可重設到任何水平,由相位位的讀取決心。該單片機處理器有長對互替的模以的讀取,配有50Ω的背后POS機終端用戶。的讀取正弦波形參數的概率可由30個概率管控位Vi[0:29]管控。的讀取正弦波形參數的相位還可完成11位Pi[0:10]相位幅度幅度調制解調解調的讀取完成幅度幅度調制解調解調。DS875可聯受差分數字秒表的讀取或單端數字秒表的讀取,并存在50Ω片上回接地線POS機終端用戶。概率字和相位字的讀取都學習LVTTL/CMOS的讀取電平。差分關聯的讀取SyncI_P/N為多種單片機處理器廣泛應用提高關聯,混用關聯的讀取的完全相同相位打火4個單片機處理器SyncO_P/N,預備學習概率字和選通的讀取。關聯選通的讀取由外部的互轉的8除數字秒表鎖存,這個數字秒表也被轉發到的讀取引腳SyncO_P/N。SyncO_P/N適采用為參看,將概率字、相位字和選通信網絡號的讀取隨機任務對標與外部的除于8數字秒表關聯,以正確性鎖存各個的讀取數據報告。重設是異步的,以是較為小的化模以的讀取能夠的性的數字秒表延長。對外部的隨機任務完成了提高,以防止在概率字和/或相位字互轉這段時間內或重設后數字秒表跑偏。DAC的模以的讀取可在普通 人保證模試(廣泛應用在首奈奎斯特k線)或重設模試(廣泛應用在首、最后和三是個奈奎斯特k線)相互間選澤。結合實際自選澤的濾波器,還可能夠的地存在從直流供電到三是個奈奎斯特k線的加寬帶的信號。只需要這個-5V供電。

熱烈歡迎來上海市立維創展新材料技術有局限公司中國官方小程序小程序!

-

欧美一区二区在线观看-亚洲精品午夜精品-亚洲激情在线-国产欧美精品

Home -

關于我們

About -

微波元器件

Microwave- AMCOM

- CUSTOM MMIC

- RF-LAMBDA

- QORVO

- MACOM

- SOUTHWEST

- NOVA射頻微波

- KRYTAR

- Aeroflex-API Tech

- Anaren

- Anritsu

- RADITEK

- North Hills

- Synergy微波

- WENTEQ

- MITEQ

- Marki

- RF-Labs

- ADI

- CREE

- UMS微波

- PULSAR微波

- MegaPhase

- JDSU光纖測試

- AMG-Microwave

- Ironwood

- Teledyne防務電子

- HEROTEK

- ARRA

- MCLI

- Leadway

- CERNEX

- Mi-Wave

- ATM Microwave(L-3)

- UTE Microwave

- NEL Frequency Controls

- API SAW Oscillators

- SemiGen

- KR Electronics

- MECA

- Electro-Photonics

- RLC Electronics

- JUPITER(Canada)

- ?IPP

-

電源模塊

Power -

DAC | ADC芯片

DAC|ADC -

微處理器

MCU -

風扇

Fan -

熱縮管

Heat Shrink Tubing -

自研產品

Leadway Prodcuts - 聯系我們

Contact

簡體中文

簡體中文

DACADC基帶芯片

DACADC基帶芯片