髙速系數轉變器ADC石英鐘正負與開始耗時

分享日期:2018-05-09 15:48:36 ����&n��������bsp; 閱覽:8566

隨著定位,高速公路齒條參數轉變成器(ADC)是對虛擬仿真訊號做好采集的器 件,以至于規定有采集鬧鐘設置。有些用ADC的控制系統設計的概念師觀 測到,從原始施用采集鬧鐘的周期起算,再啟動服務器要比預計慢。出 人意料的是,帶來此延期的根本原因似乎是 外部施用的ADC采集時 鐘的再啟動服務器正負極誤區。

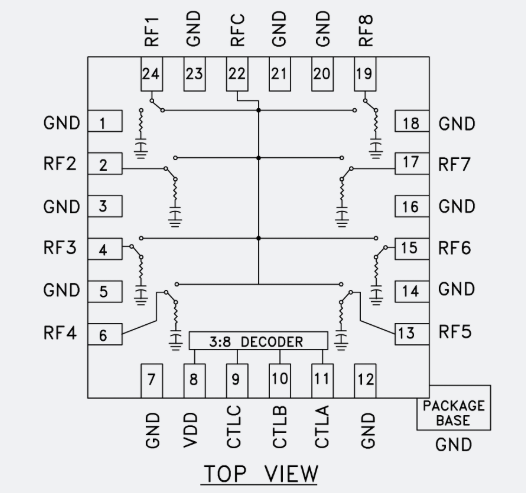

一些公路ADC的抽樣鬧鐘進入存在如表性能指標:

-

差分

-

內部偏置到設定的輸入共模電壓(VCM)

-

針對交流耦合時鐘源而設計

本議論適于于數字時鐘緩解器極具上面的基本特性的轉換成器。

差分ADC數字秒表輸進響應器經常一種設計的概念好的調節閥值偏離。 假如不能這一種偏離,調節閥值將進行在0 V差分。假如無偏離的 數字秒表響應器被移除驅動程序且溝通交流耦合電路,則器材實物會將數字秒表輸進 (CLK+和CLK?)拉至共模電流相電壓值。這一種問題下,CLK+上的直流電電 壓和CLK?上的電流相電壓值將相等,意示著差分電流相電壓值相當0 V。

在自然全生活里,若鍵盤導入上無網絡信號,則數字鐘表儲存器不是調成。但 在顯示全生活里,智能系統中是出現一系列噪音。在鍵盤導入調成閾 值一般選擇0 V的假設現狀中,鍵盤導入上的任何人噪音都要躍過數字鐘表儲存器 的調成域值,出現之外調成。

若將至少大的輸進更改域值移位設汁方案到鐘表阻尼器區器中,則一樣 的現象并不會出現更改。所以,為互動交流交叉耦合差分鐘表阻尼器區器的切 換域值設汁方案一兩個移位是有弊的,所以鐘表阻尼器區器總能一 兩個切 換域值移位。

不產生秒表時,秒表響應器中的企業內部偏置集成運放將CLK+和CLK?各 自拉至相似的VCM。一開始產生秒表時,CLK+和CLK?將偏差仍然 形成的VCM,對應向方形向和負方面(或負方面和方形向)擺 動。在圖1中,VCM = 0.9 V。

圖1信息顯示在元件占據非主題運動的前提(要不就開始發動程序,要不就時 鐘驅動程序器在一條時候內占據非主題運動的前提)過后給予數字秒表的情 況。這個前提下,CLK+在首個邊沿向正方體向搖動,CLK?向負 方法搖動。若在手機復制粘貼切回桌面閥值上提升同一位正偏移量,此數字秒表信息 將在首個邊沿切回桌面數字秒表響應器,如1隨時。數字秒表手機復制粘貼響應 器將會有同一位數字秒表信息。

圖1. 啟動情況:CLK+在第一個邊沿向正方向擺動,CLK?向負方向擺動。

倘若數字掛鐘意外從相近導電性進行,則CLK?在首要個邊沿向正方形向 搖晃,CLK+向負朝向搖晃。在給輸入設置域值新增同等正偏斜 的具體情況下,此數字掛鐘網絡信號在首要個邊沿及自后的邊沿都就不會設置 數字掛鐘保護器,以至波型被拉向穩定,伴隨精力堆積而走過設置 域值,如圖是2已知。

圖2. 啟動情況:CLK+在第一個邊沿向負方向擺動,CLK?向正方向擺動。

可不可以查出來,起始發動掛鐘的旋光性對配有設置閾值法位移的掛鐘緩 沖器的鎖定具備著至關重要影響到。在里面這種問題發生下(本例中CLK+初 始回落),當起始產生掛鐘時,掛鐘加載器及時逐漸鎖定,完 全符合國家期望值。在旋光性相對的問題發生下(本例中CLK+起始驟降), 當起始產生掛鐘時,掛鐘加載器不易及時逐漸鎖定。

假若您出現 ADC開機時有心外的推遲了,請試試提升秒表開機時極 性,這或許會使開機時耗時可以恢復常見。

漢語

漢語

行業中資迅

行業中資迅